MCU

STM32驱动WS2812

vulnhub

arm开发

费用流

项目管理

kinect

SAP ABAP

gitlab

DOM型XSS

资源

IT企业管理基本概念

进程同步

camera

征文

宠物

天鹰算法优化随机森林多分类

Conditional注解

项目实战

antdb数据库

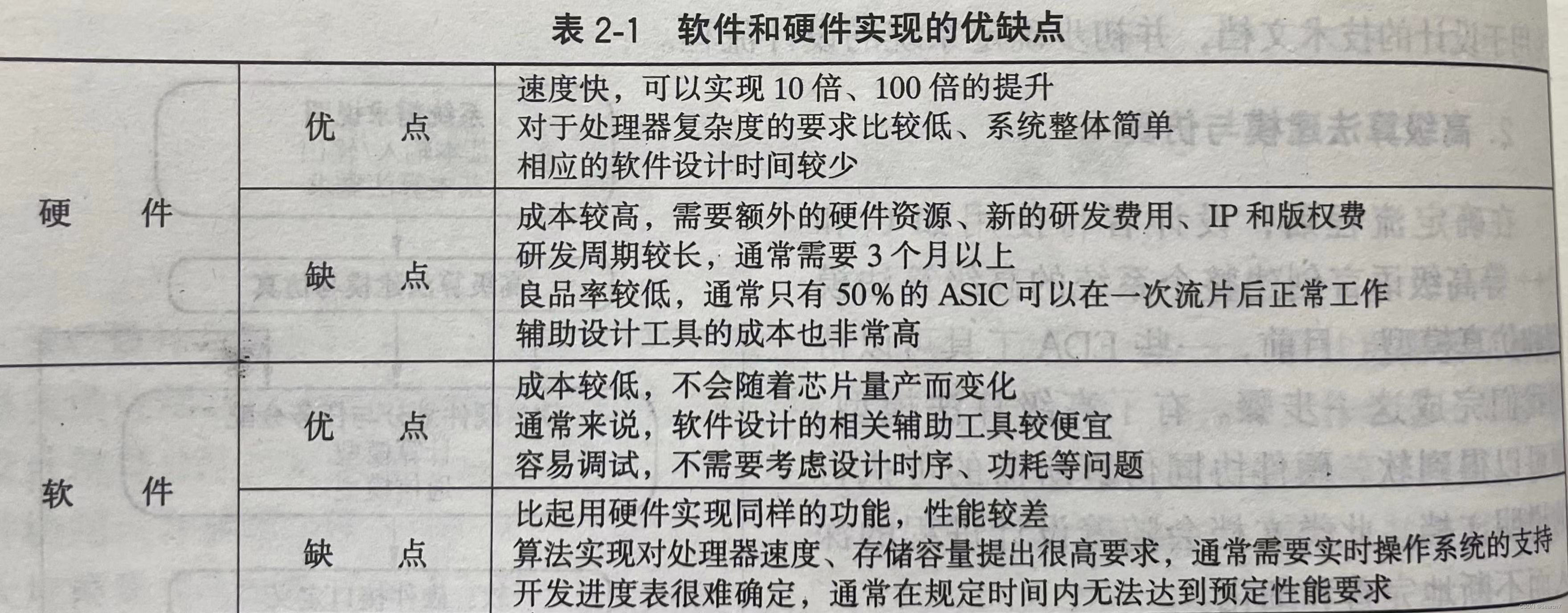

SOC设计

2024/4/11 21:18:05有必要好好学习一下dc_shell了

首先最好是有design compiler user guide,哪里不会找哪里?然后来看看常见的dc_shell 命令

一般先要起一个dc_shell。 dc_shell 启动以后,使用 read_ddc xxx/DBs/ddc/<block_name>.ddc 将design compiler的综合结果读入。

为了确认读入…

Lib文件和netlist的关系,DDC文件和netlist的区别

今天来说一说两个基础的概念:

1:综合用的Lib文件和netlist网表的关系

在数字IC设计中,Lib和网表都是非常重要的文件,但它们的作用和用途有很大的区别。

Lib文件,也称为库文件,主要包含单元级的信息&…

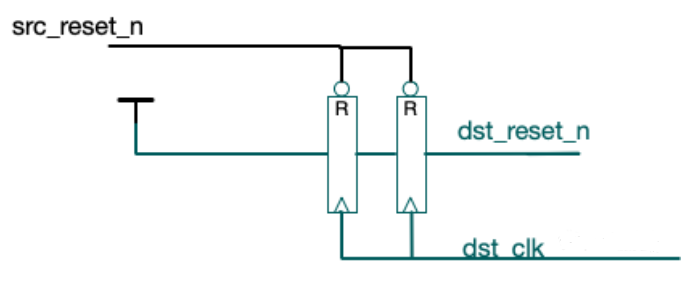

Reset信号如何同步?

首先来复习一个更加基础的概念:同步reset和异步reset。

同步reset(synchronous reset)是说,当reset信号为active的时候,寄存器在下一个时钟沿到来后被复位,时钟沿到来之前寄存器还是保持其之前的值。

异步…

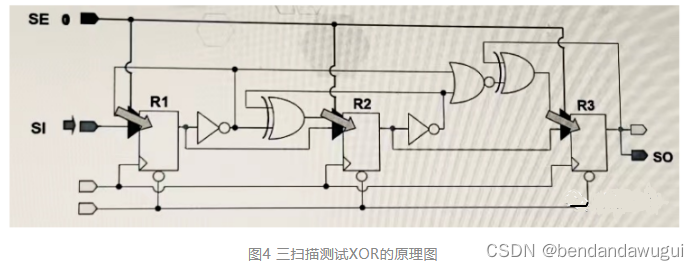

DFT简单介绍以及CP和FT测试介绍

相信很多ICer在Light芯片的过程中无论前端还是后端都听过DFT设计测试,DFT全称Desigh for Test(即可靠性设计),众所周知,测试的目的是为了保证芯片成品的质量以及功能逻辑的可靠性的必须措施,在十年前&#…

数字IC后端实现 |TSMC 12nm 与TSMC 28nm Metal Stack的区别

下图为咱们社区IC后端训练营项目用到的Metal Stack。

芯片Tapeout Review CheckList 数字IC后端零基础入门Innovus学习教程 1P代表一层poly,10M代表有10层metal,M5x表示M2-M6为一倍最小线宽宽度的金属层,2y表示M7-M8为二倍最小线宽宽度的金…

SOC设计:关于时钟门控的细节

有如下几个信号

输入信号

1、同步后的rstnsync_clk

2、时钟:clk

3、test_mode

4、软件控制信号:clk_sub_en

输出信号

1、clk_sub

功能:软件配置的使能信号clk_sub_en经过时钟clk 2拍同步处理后产生clk 域下的enable信号,然…

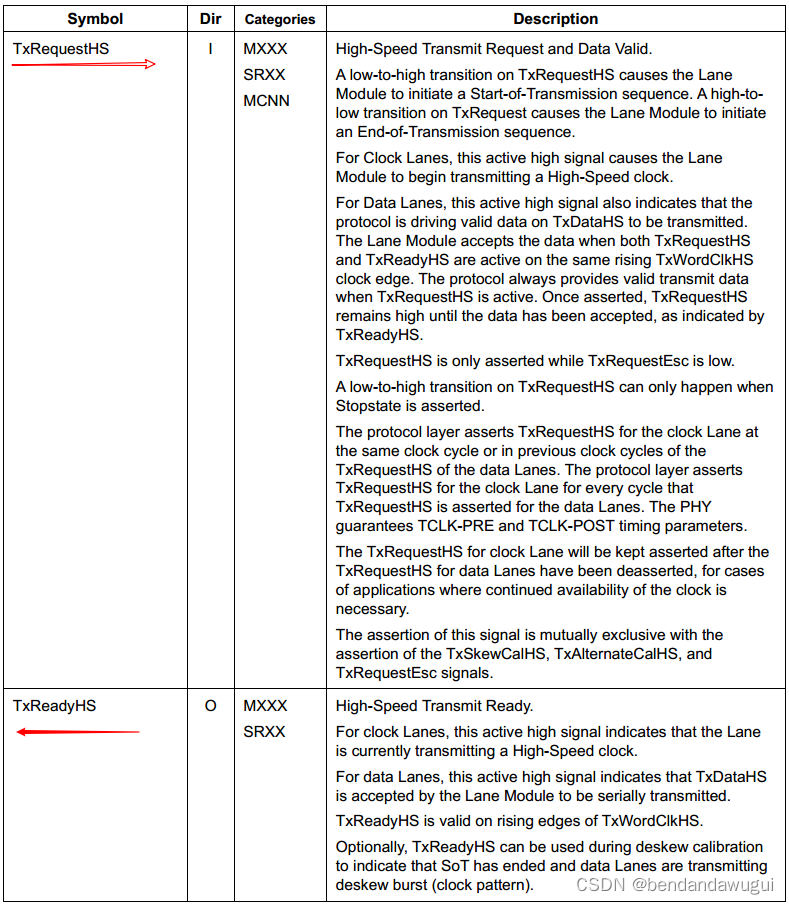

mipi DPHY学习记录

DPHY的内容很多,而且细节很多,我会一点一点的进行补充记录,今天要记录的是cdphy的LP-MODE数据传输的过程。

1:HS 和LP mode lane status 和 lane上的电压 HS mode时,差分线上的电压摆幅为200mv,LP mode时,差分线上的电压为1.2v

2:HS mode data Transmission start

在…

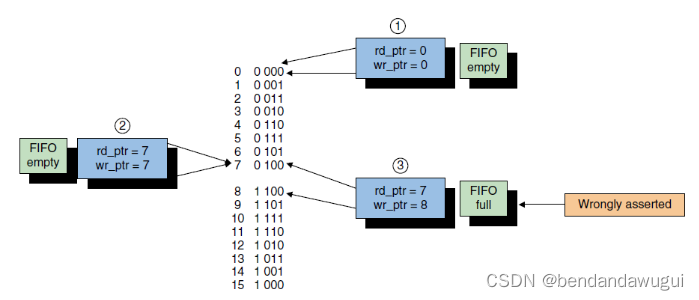

来讲一讲面试必问的异步FIFO设计!

异步FIFO设计可以说是数字IC设计工程师面试时必问的一个问题了,也是我们经常使用但是又往往被忽略的一个东西,今天就展开详细说一说不同深度(2^N或者非2^N)异步FIFO的设计思想;

一:2^N深度异步FIFO设计

1…

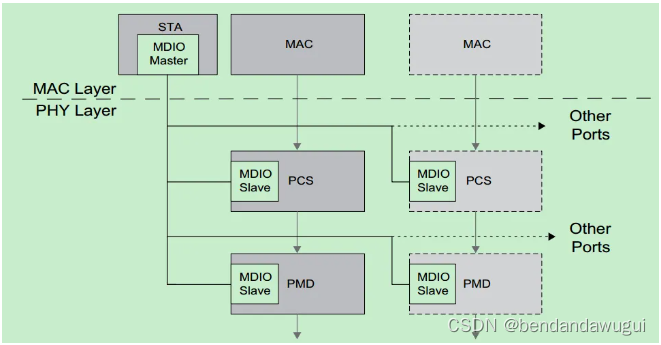

以太网PHY,MAC及其通信接口介绍

本文主要介绍以太网的 MAC 和 PHY,以及之间的 MII(Media Independent Interface ,媒体独立接口)和 MII 的各种衍生版本——GMII、SGMII、RMII、RGMII等。

一:简介

从硬件的角度看,以太网接口电路主要由MA…

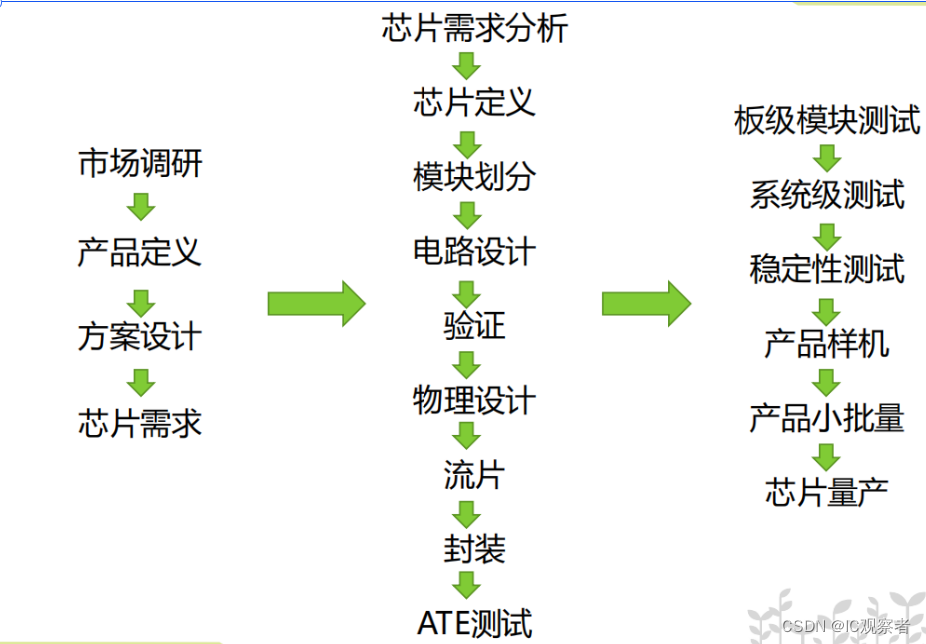

芯片SoC设计你了解吗?

数字IC设计根据岗位性质一般包含SOC设计,前端设计,ASIC设计,逻辑设计,IP设计,CPU设计等。 有人说:做IP设计就是翻译官,做SOC设计就是连连看。 SoC设计是做什么的?与IP设计有什么不同…

SOC设计:关于reset的细节

有如下几个信号

1、时钟:clk_top

2、总的reset信号:rstn_top

3、scan的reset信号:scan_rstn

4、软件复位信号:rstn_soft_sub

5、scan模式信号:scan_mode

6、reset bypass 信号:scan_rstn_sel

功能&a…

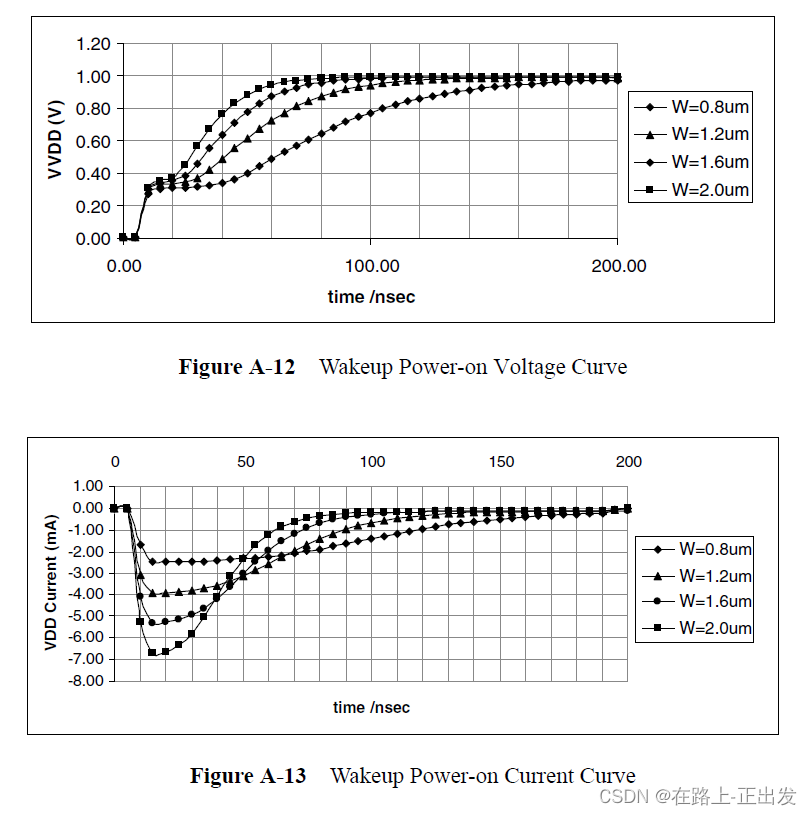

《低功耗方法学》翻译——附录A:睡眠晶体管设计

附录A:睡眠晶体管设计

休眠晶体管是PMOS或NMOS高VT晶体管,用于在待机模式下关闭设计部件的电源。PMOS休眠晶体管用于切换VDD电源,因此被称为“header开关”。NMOS休眠晶体管控制VSS电源,因此被称为“footer开关”。在90 nm及以下…

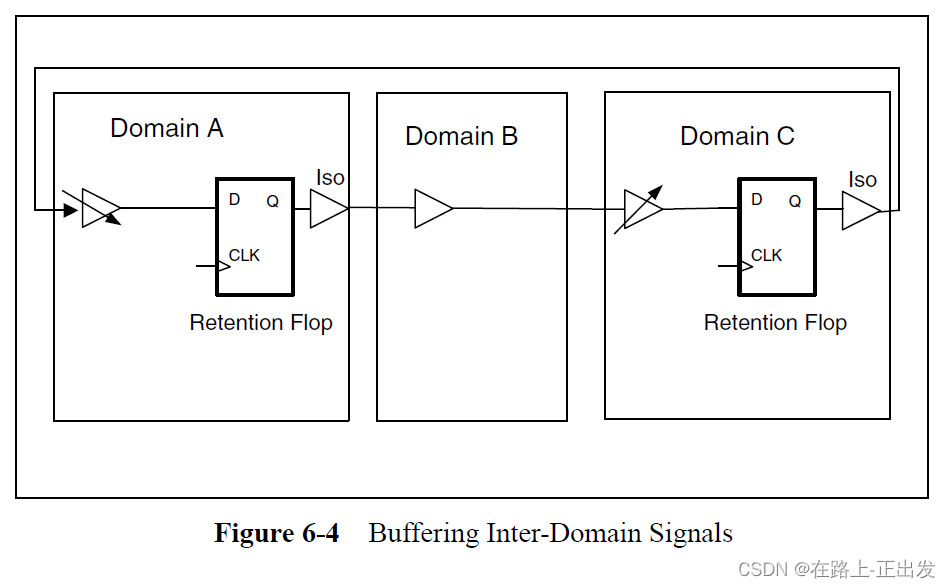

《低功耗方法学》翻译——第六章:功率门控的架构问题

第六章:功率门控的架构问题

本章讨论了植入功率门控设计中涉及的一些架构问题。特别地,它解决了分区、层次结构和多个功率门控域的问题。

6.1 层次化结构和功率门控

芯片架构的可扩展方法是有价值的,因为今天在芯片上的系统设计经常在随后…

systemverilog function的一点小case

关于function的应用无论是在systemverilog还是verilog中都有很广泛的应用,但是一直有一个模糊的概念困扰着我,今天刚好有时间来搞清楚并记录下来。

关于fucntion的返回值的问题:

function integer clog2( input logic[255:0] value);for(cl…